晶振官方博客

更多>>SiTime振蕩器時(shí)間誤差模擬

來(lái)源:http://m.dxwyp.cn 作者:康華爾電子 2019年07月27

自電信業(yè)出現(xiàn)以來(lái),網(wǎng)絡(luò)同步一直是語(yǔ)音通信的重要因素.早期,采用頻率同步來(lái)確保高質(zhì)量和高可靠性的電話呼叫.在今天的網(wǎng)絡(luò)中,數(shù)據(jù)流量消耗了大部分網(wǎng)絡(luò)帶寬.雖然語(yǔ)音通信現(xiàn)在只占網(wǎng)絡(luò)帶寬的一小部分,但仍需要頻率和時(shí)間/相位同步來(lái)確保網(wǎng)絡(luò)運(yùn)行和可靠性.當(dāng)網(wǎng)絡(luò)開(kāi)始使用時(shí)分雙工(TDD)時(shí),時(shí)間同步變得很重要.隨著即將推出的5G,非常緊密的時(shí)間/相位同步以及晶振頻率同步對(duì)于這些網(wǎng)絡(luò)來(lái)說(shuō)將是必不可少的,以提高數(shù)據(jù)吞吐量以支持新興應(yīng)用的需求,例如自動(dòng)駕駛,遠(yuǎn)程手術(shù)和更精確的地理定位.

位于網(wǎng)絡(luò)節(jié)點(diǎn)中的本地振蕩器在系統(tǒng)的整體同步性能中起著至關(guān)重要的作用.這適用于使用同步以太網(wǎng)的頻率同步系統(tǒng),使用IEEE 1588中描述的精確時(shí)間協(xié)議(PTP)的時(shí)間/相位/頻率同步系統(tǒng),或兩者的組合.在5G網(wǎng)絡(luò)中,嚴(yán)格的時(shí)間對(duì)齊要求在整個(gè)系統(tǒng)中至關(guān)重要.基站天線的對(duì)準(zhǔn)要求可以非常緊湊,低至65納秒(ns),具體取決于MIMO,載波聚合和發(fā)射機(jī)分集.此外,回程網(wǎng)絡(luò)(網(wǎng)絡(luò)交換機(jī),路由器)中每個(gè)網(wǎng)絡(luò)節(jié)點(diǎn)所允許的添加的定時(shí)錯(cuò)誤量可以低至每個(gè)節(jié)點(diǎn)5ns.

在這種同步系統(tǒng)中,在每個(gè)網(wǎng)絡(luò)節(jié)點(diǎn)處存在本地石英晶體振蕩器,其提供時(shí)鐘到同步鎖相環(huán)(PLL).PLL環(huán)路帶寬通常設(shè)置在1mHz至0.1Hz的范圍內(nèi),具體取決于實(shí)現(xiàn)方式.許多因素會(huì)影響時(shí)間錯(cuò)誤性能.本地振蕩器的穩(wěn)定性是節(jié)點(diǎn)中產(chǎn)生的時(shí)間誤差的主要原因.PLL濾波功能(PLL環(huán)路順序,PLL環(huán)路帶寬)和輸入信號(hào)中的漂移量也是影響因素.

使用實(shí)時(shí)數(shù)據(jù)進(jìn)行實(shí)際時(shí)間錯(cuò)誤分析是一個(gè)復(fù)雜而漫長(zhǎng)的過(guò)程,執(zhí)行時(shí)間從幾周到幾個(gè)月不等.為了幫助緩解這些問(wèn)題,SITIME晶振公司開(kāi)發(fā)了時(shí)間誤差模擬器軟件,模擬本地振蕩器的不穩(wěn)定性產(chǎn)生多少漂移,前提是參考輸入是理想的并且是自由漂移的.該工具可以在各種不同的系統(tǒng)參數(shù)和溫度曲線下快速模擬時(shí)間誤差.

SiTime Time Error Simulator軟件需要振蕩器的基本性能數(shù)據(jù)的以下三個(gè)區(qū)域(在組件級(jí)別測(cè)量):

1.振蕩器的頻率超溫行為-模擬溫度變化的貢獻(xiàn).

2.振蕩器的頻率隨時(shí)間變化的行為(頻率趨勢(shì)至少1小時(shí))-模擬振蕩器的漂移貢獻(xiàn).

3.一天頻率老化-模擬振蕩器的老化貢獻(xiàn).

這些數(shù)據(jù)可以在實(shí)驗(yàn)室中獲得,不超過(guò)一天的數(shù)據(jù)捕獲.或者,它可以由有源晶體振蕩器供應(yīng)商提供.根據(jù)用戶PC的性能,24小時(shí)頻率老化可能只需半小時(shí)的仿真時(shí)間,這比實(shí)時(shí)測(cè)量快得多.本文討論了用于時(shí)間誤差的各種模型使用STime Error Simulator軟件模擬PTP和PTP+SyncE應(yīng)用程序.

1.僅PTP仿真模型

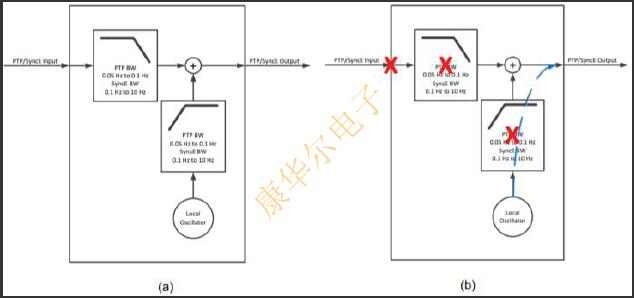

僅PTP仿真模式模擬本地水晶振蕩子頻率變化對(duì)沒(méi)有物理層頻率支持的單個(gè)電信時(shí)鐘(如T-BC)的性能的影響.這種情況下的模型是單個(gè)PLL模型.時(shí)間誤差模擬器軟件支持兩種時(shí)鐘狀態(tài)的模擬:鎖定狀態(tài)和保持.圖1顯示了這兩種時(shí)鐘狀態(tài)的仿真模型圖. PLL模型的輸入是本地振蕩器隨時(shí)間的頻率特性.可以選擇許多本地SPXO振蕩器頻率變化的因素:可變溫度效應(yīng),振蕩器漂移效應(yīng)和日常老化效應(yīng).

對(duì)于鎖定狀態(tài)模擬,假設(shè)PTP輸入是理想的,因此時(shí)間誤差為0.該方法用于模擬本地振蕩器不穩(wěn)定性的貢獻(xiàn).本地振蕩器的頻率隨時(shí)間變化趨勢(shì)用于計(jì)算理想時(shí)鐘的頻率誤差.該頻率誤差被積分以計(jì)算時(shí)間誤差.然后,將本地振蕩器對(duì)PLL輸出的貢獻(xiàn)模型應(yīng)用于時(shí)間誤差,以模擬PLL輸出的結(jié)果時(shí)間誤差.本地振蕩器對(duì)PLL輸出影響的簡(jiǎn)化模型是高通濾波器,其截止頻率與環(huán)路濾波器帶寬相同.過(guò)濾帶寬和訂單參數(shù)由用戶定義.

對(duì)于保持狀態(tài)模擬,假定同步誤差(進(jìn)入保持之前的時(shí)間誤差)為0.當(dāng)失去對(duì)主控的鎖定時(shí),PLL輸出跟隨本地振蕩器,因此低電壓有源晶振貢獻(xiàn)的PLL模型降低到單位增益常數(shù).由于軟件生成通用PLL仿真,因此僅PTP仿真模式也可用于估計(jì)SyncEe EEC性能.但是,時(shí)鐘帶寬會(huì)有所不同.在電信應(yīng)用中,PTP帶寬通常在幾mHz到20mHz之間,而SyncE帶寬在0.1Hz到10Hz之間.

位于網(wǎng)絡(luò)節(jié)點(diǎn)中的本地振蕩器在系統(tǒng)的整體同步性能中起著至關(guān)重要的作用.這適用于使用同步以太網(wǎng)的頻率同步系統(tǒng),使用IEEE 1588中描述的精確時(shí)間協(xié)議(PTP)的時(shí)間/相位/頻率同步系統(tǒng),或兩者的組合.在5G網(wǎng)絡(luò)中,嚴(yán)格的時(shí)間對(duì)齊要求在整個(gè)系統(tǒng)中至關(guān)重要.基站天線的對(duì)準(zhǔn)要求可以非常緊湊,低至65納秒(ns),具體取決于MIMO,載波聚合和發(fā)射機(jī)分集.此外,回程網(wǎng)絡(luò)(網(wǎng)絡(luò)交換機(jī),路由器)中每個(gè)網(wǎng)絡(luò)節(jié)點(diǎn)所允許的添加的定時(shí)錯(cuò)誤量可以低至每個(gè)節(jié)點(diǎn)5ns.

在這種同步系統(tǒng)中,在每個(gè)網(wǎng)絡(luò)節(jié)點(diǎn)處存在本地石英晶體振蕩器,其提供時(shí)鐘到同步鎖相環(huán)(PLL).PLL環(huán)路帶寬通常設(shè)置在1mHz至0.1Hz的范圍內(nèi),具體取決于實(shí)現(xiàn)方式.許多因素會(huì)影響時(shí)間錯(cuò)誤性能.本地振蕩器的穩(wěn)定性是節(jié)點(diǎn)中產(chǎn)生的時(shí)間誤差的主要原因.PLL濾波功能(PLL環(huán)路順序,PLL環(huán)路帶寬)和輸入信號(hào)中的漂移量也是影響因素.

使用實(shí)時(shí)數(shù)據(jù)進(jìn)行實(shí)際時(shí)間錯(cuò)誤分析是一個(gè)復(fù)雜而漫長(zhǎng)的過(guò)程,執(zhí)行時(shí)間從幾周到幾個(gè)月不等.為了幫助緩解這些問(wèn)題,SITIME晶振公司開(kāi)發(fā)了時(shí)間誤差模擬器軟件,模擬本地振蕩器的不穩(wěn)定性產(chǎn)生多少漂移,前提是參考輸入是理想的并且是自由漂移的.該工具可以在各種不同的系統(tǒng)參數(shù)和溫度曲線下快速模擬時(shí)間誤差.

SiTime Time Error Simulator軟件需要振蕩器的基本性能數(shù)據(jù)的以下三個(gè)區(qū)域(在組件級(jí)別測(cè)量):

1.振蕩器的頻率超溫行為-模擬溫度變化的貢獻(xiàn).

2.振蕩器的頻率隨時(shí)間變化的行為(頻率趨勢(shì)至少1小時(shí))-模擬振蕩器的漂移貢獻(xiàn).

3.一天頻率老化-模擬振蕩器的老化貢獻(xiàn).

這些數(shù)據(jù)可以在實(shí)驗(yàn)室中獲得,不超過(guò)一天的數(shù)據(jù)捕獲.或者,它可以由有源晶體振蕩器供應(yīng)商提供.根據(jù)用戶PC的性能,24小時(shí)頻率老化可能只需半小時(shí)的仿真時(shí)間,這比實(shí)時(shí)測(cè)量快得多.本文討論了用于時(shí)間誤差的各種模型使用STime Error Simulator軟件模擬PTP和PTP+SyncE應(yīng)用程序.

1.僅PTP仿真模型

僅PTP仿真模式模擬本地水晶振蕩子頻率變化對(duì)沒(méi)有物理層頻率支持的單個(gè)電信時(shí)鐘(如T-BC)的性能的影響.這種情況下的模型是單個(gè)PLL模型.時(shí)間誤差模擬器軟件支持兩種時(shí)鐘狀態(tài)的模擬:鎖定狀態(tài)和保持.圖1顯示了這兩種時(shí)鐘狀態(tài)的仿真模型圖. PLL模型的輸入是本地振蕩器隨時(shí)間的頻率特性.可以選擇許多本地SPXO振蕩器頻率變化的因素:可變溫度效應(yīng),振蕩器漂移效應(yīng)和日常老化效應(yīng).

對(duì)于鎖定狀態(tài)模擬,假設(shè)PTP輸入是理想的,因此時(shí)間誤差為0.該方法用于模擬本地振蕩器不穩(wěn)定性的貢獻(xiàn).本地振蕩器的頻率隨時(shí)間變化趨勢(shì)用于計(jì)算理想時(shí)鐘的頻率誤差.該頻率誤差被積分以計(jì)算時(shí)間誤差.然后,將本地振蕩器對(duì)PLL輸出的貢獻(xiàn)模型應(yīng)用于時(shí)間誤差,以模擬PLL輸出的結(jié)果時(shí)間誤差.本地振蕩器對(duì)PLL輸出影響的簡(jiǎn)化模型是高通濾波器,其截止頻率與環(huán)路濾波器帶寬相同.過(guò)濾帶寬和訂單參數(shù)由用戶定義.

對(duì)于保持狀態(tài)模擬,假定同步誤差(進(jìn)入保持之前的時(shí)間誤差)為0.當(dāng)失去對(duì)主控的鎖定時(shí),PLL輸出跟隨本地振蕩器,因此低電壓有源晶振貢獻(xiàn)的PLL模型降低到單位增益常數(shù).由于軟件生成通用PLL仿真,因此僅PTP仿真模式也可用于估計(jì)SyncEe EEC性能.但是,時(shí)鐘帶寬會(huì)有所不同.在電信應(yīng)用中,PTP帶寬通常在幾mHz到20mHz之間,而SyncE帶寬在0.1Hz到10Hz之間.

正在載入評(píng)論數(shù)據(jù)...

相關(guān)資訊

- [2022-09-07]出色穩(wěn)定性能的5032mm石英晶體振蕩器X1...

- [2022-08-01]diodes晶振專用于時(shí)間顯示設(shè)備的32.768...

- [2022-07-27]伊西斯的新型且創(chuàng)意的低姿態(tài)TCXO晶體振...

- [2020-06-22]深入探討有源晶振8個(gè)基礎(chǔ)參數(shù)詞匯

- [2020-05-25]SiTime開(kāi)發(fā)的新軟件可模擬振蕩器時(shí)間誤...

- [2020-05-12]微處理器應(yīng)該怎樣選擇匹配晶振?一文足...

- [2020-04-14]NDK株式會(huì)社差分振蕩器NP3225SBB規(guī)格更...

- [2020-03-13]不同類型的Crystal Oscillator工作與電...

- [2019-11-09]了解EPSON晶振獨(dú)特的封裝技術(shù)

- [2019-09-21]NDK振蕩器電路圖介紹及安裝示例

- [2019-09-16]擁有聲子晶體結(jié)構(gòu)的AT切割諧振器共振分...

- [2019-09-04]SMD Oscillator高溫回流焊接的滯后反應(yīng)...

銷售代表

銷售代表 售后服務(wù)

售后服務(wù)

.jpg)

.jpg)